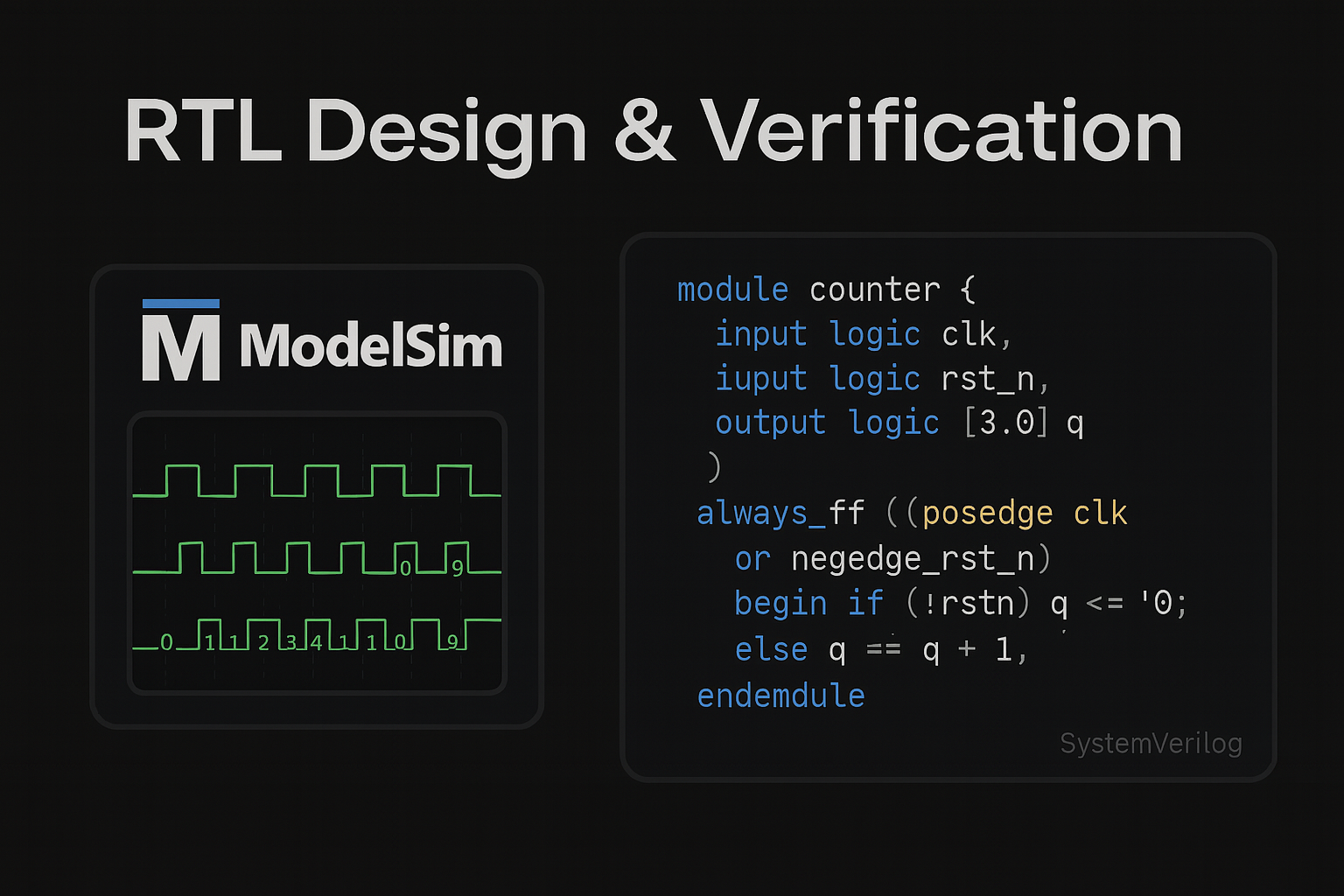

The goal of this project was to design and verify the ASCON128 cipher, a lightweight authenticated encryption algorithm (AEAD). The focus was on building a correct and modular RTL design in SystemVerilog and validating its functionality through behavioral simulation using ModelSim.

System Architecture

ASCON128 operates on a 320-bit internal state divided into five 64-bit words. The encryption process includes several phases: initialization, associated data processing, plaintext encryption, and finalization with authentication tag generation.

To implement this algorithm in RTL, the project was divided into the following components:

Constant Addition (PC) – injects round constants into the state during each round.

Substitution Layer (PS) – applies parallel 5-bit S-box transformations.

Diffusion Layer (PL) – spreads information across the state for proper mixing.

Permutation Engine – executes sequences of 6 or 12 rounds, combining the above layers.

XOR Modules & Registers – handle integration of keys, plaintext, and associated data.

FSM (Finite State Machine) – controls the sequencing of operations (partially implemented for initialization).

The permutation core with all its components (constants, S-box, diffusion, XORs, and registers) was fully implemented and verified against reference values.

Used Tools

SystemVerilog for RTL design

ModelSim for compilation and simulation of testbenches

- VS Code for source code management and organization